|

Особенности процессорной разработки

Планируя создание устройства целевого назначения разработчику необходимо найти компромисс, между специализацией системы, и ее универсальностью, используя принципы разумной достаточности.

Подходы

Наилучший способ для достижения «золотой середины» - разработка программных и аппаратных средств, в рамках единого проекта, который состоит из

• набора системной логики;

• BIOS;

• специализированной операционной системы;

• модульных аппаратно-ориентированных приложений.

Системная логика: отказ от стереотипов

Так повелось, что, обсуждая ту или иную архитектуру чипсета, в первую очередь рассматривается организация адресного пространства и его распределение между системной памятью и портами вводавывода. Традиционный подход, применяющийся в персональных компьютерах, налагает ряд ограничений на оба способа доступа к имеющимся ресурсам. Это чаще всего определяется требованиями совместимости аппаратного и программного обеспечения. Но современные тенденции таковы, что проекция пространства памяти и пространства портов вводавывода должна выполняться в общее адресное пространство на условиях инвариантности. Конкретная реализация должна опираться на использование одного или обоих способов, что диктуется эффективностью обработки потоков данных.

Второй существенный фактор, который отличает персональные компьютеры от целевых встроенных устройств – это отношение к размеру и типу используемой памяти.

Пользователь персонального компьютера может самостоятельно принять решение об объеме используемой памяти, исходя из собственных соображений целесообразности, основанных на таких параметрах как рыночная стоимость, влияние на производительность программного обеспечения и т.п.

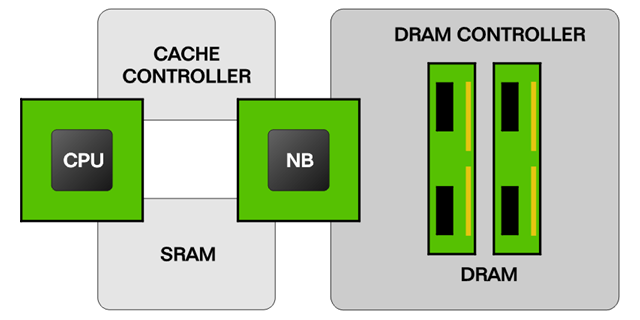

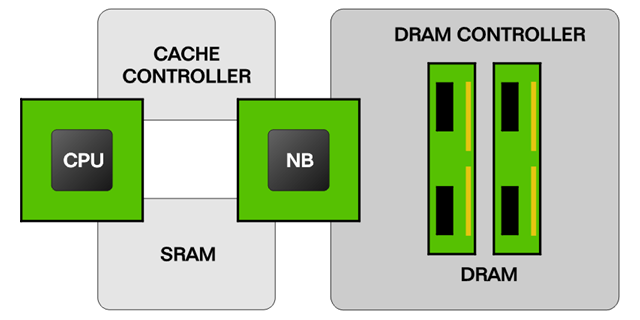

Применительно к встроенным устройствам вопрос о размере ставиться подругому: сколько памяти нужно для решения поставленной задачи. Вопрос о типе тоже выглядит иначе: какой тип памяти поможет решить задачу наилучшим образом, как это скажется на себестоимости конечного продукта, насколько это усложнит или упростит разработку. Наши исследования показали, что в подобных устройствах можно отказаться от использования DRAM (FPM, EDO, SDRAM) в пользу SRAM, получив такие преимущества, как быстродействие, и, самое главное, простота и надежность схемных решений. На себестоимость изделия, в равной степени, влияет как общая стоимость компонентов, так и время потраченное на его создание, определяющее такой немаловажный показатель, как TimeToMarket.

Процессор: поиск альтернатив

Выбор процессора для разработчика целевых устройств – всегда непростая задача. При всем многообразии предложения на рынке, она сводится к поиску приемлемого решения в одной из двух групп: CISC и RISC. Традиционная архитектура с полным набором команд CISC в процессе технической эволюции «обросла» некоторыми дополнительными возможностями. В чип процессора встраиваются и системные контроллеры, и контроллеры периферийных устройств (UART, ISDN, HDLC, цифроаналоговые преобразования и т.п.). Эти процессора становятся наиболее вероятными кандидатами для реализации встроенных систем, но зачастую страдают избыточностью. Например, CISC выполненный как SystemOnChip (SOC), может обеспечить необходимый последовательный порт, Ethernet, но заодно мы получаем и невостребованный видеовыход, параллельный порт и т.д. Нелишне отметить, что цена таких процессоров значительно выше по сравнению со своими прототипами без таких возможностей.

К достоинствам RISC можно отнести большое разнообразие моделей, что позволяет оптимально выбрать необходимый процессор, в котором интегрировано только то, что нужно для данного проекта. Недостатки этих процессоров весьма существенны, и, как говорится, являются продолжением их достоинств. Это ограниченный набор программного обеспечения, низкая совместимость на уровне кода, непродолжительное время жизни моделей, отсутствие альтернативных «вторых» источников производства микросхем, невозможность разработки программного обеспечения на персональных компьютерах без применения эмуляторов. Весьма существенен и «человеческий фактор» сложно найти специалистов, умеющих работать с той или иной реализацией RISC процессора. Как следствие значительные потери времени на приобретение профессиональных навыков в постижении тонкостей конкретной модели.

Если разрабатываемое устройство достаточно сложное, то решающим фактором становятся сроки разработки, ну и конечно цена. При таком подходе можно использовать все преимущества CISC процессоров, в первую очередь, разработку программного обеспечения и отладку макетов на персональном компьютере. В этом случае акцент в разработке целевого устройства переносится на создание простого и эффективного набора системной логики.

Интеграция

Исходя из предпосылки, что разработка проекта включает в себя и работы по созданию системной логики, мы остановились на 16ти разрядном CISC процессоре, совместимом по программной модели с i286 Intersil 80C28625. Работа в этом направлении может продолжаться на любых устройствах семейства x86.

Планируя архитектуру чипсета, мы учитывали современные тенденции в построении шинных топологий. В результате была разработана системная шина sLPC (Simplified Low Pin Count), позволяющая достаточно просто реализовать подключение стандартных PCI устройств. Это открывает возможности по использованию готовых решений от Realtek, Myson и др. Хотя такой тандем выглядит несколько парадоксально, это не мешает вести полноценный обмен данными между процессором и PCI устройствами. Реализована поддержка ряда дополнительных стандартов, необходимых для их конфигурирования (PnP).

По аналогии с архитектурой персональных компьютеров хостконтроллер можно назвать Северным Мостом. Он управляет движением потоков данных между процессором, памятью и sLPC. К sLPC подключены как периферийные устройства, такие как асинхронные порты, так и локальные шины. Доступ к ним обеспечивают дополнительные мосты, которые аналогичные Южными Мостам. Структура шины sLPC и Южных Мостов достаточно простая, поэтому данные передаются от процессора к PCI устройствам практически с такой же скоростью, как и при работе с памятью. При таком построении, по сути, нет ограничений на количество подключаемых PCI устройств и Южных Мостов. Это позволяет достаточно просто создавать масштабируемые многоканальные целевые системы.

BIOS

Опыт, полученный в процессе разработки LiteBIOS для систем диагностики материнских плат, сыграл решающую роль в проектировании собственной системы вводавывода и процедур инициализации.

Сократить сроки выпуска BIOS позволяет применение хорошо зарекомендовавшая себя практика работы с диагностическими POST кодами и отладочными модулями визуализации выполнения программ.

Такой подход позволяет выполнять оперативную трассировку приложений при отладке и сокращает сроки разработки.

Операционная система

Нацеленность на решение конкретных задач и отказ от использования дорогостоящих компонентов ставят жесткие требования к производительности операционной системы.

По этой причине выбор архитектуры x86 считаем эффективным, так как разработка и отладка может вестись на реальных PC совместимых платформах в среде MS DOS или Windows 9x, а использование языка ассемблера позволяет оптимизировать исполняемый код.

Совершенно очевидно, что для решения задач в мультипротокольной информационной среде требуется многозадачная операционная система. Однако этого, зачастую, недостаточно. Назначение многозадачной ОС состоит в разумном разделении времени между выполняемыми в ней приложениями. В случае, когда приложения значительно отличаются друг от друга по ресурсоемкости, приходится не только разделять процессорное время между приложениями, но и сами приложения строить особым образом, обеспечивающими возможность приостанавливать свое выполнение для того, чтобы дать возможность активной задаче выполнить свою работу обеспечить так называемый Time Slicing.

При разработке целевой ОС во главу угла ставятся три основных фактора быстродействие, отказоустойчивость и минимизация реакции на внешнее воздействие. Если первый фактор обеспечивается оптимизацией программного кода, то Time Slicing обеспечивает второй и третий факторы.

Для обслуживания макета была разработана много ранговая операционная система. Основной модуль ядро, который контролирует и отвечает за взаимодействие между модулями драйверов, обработчиками прерываний, приложениями и т.д. Взаимодействие осуществляется с помощью флагов. Каждому модулю для работы с данными выделяется своя локальная область памяти. Такой подход позволяет снизить вероятность возникновения перекрестных ссылок.

Обработчики прерываний оперируют только флагами, не занимаясь обслуживанием аппаратных модулей. Это в значительной степени повышает устойчивость операционной системы к сбоям в потоке данных, превышающего пропускную способность целевого устройства, либо в результате отказа одного из программных или аппаратных модулей.

Драйвера, базируясь на технологии Time Slice, позволяют оперировать с большим количеством подключенных аппаратных модулей.

Аппаратноориентированные приложения

Единая архитектура приложений должна строится по тем же принципам, по которым разработана системная логика. Такой подход позволяет в дальнейшем ряд ресурсоемких задач, таких как TCP/IP стек и другие, использовать не в программном представлении, а как TaskOnChip, т.е. как автономное аппаратное решение.

Следует отметить, что жесткие требования к производительности накладывают ряд ограничений на реализацию прикладных задач. По этой причине их структура, строится на основе приоритетов исполнения, обладая в то же время равными правами на уровне драйверов и интерфейсных процедур.

Концепция сценариев для управления каналами

Сложился стереотип, что целевые устройства не способны совершать сложные законченные действия, которые присущи персональным компьютерам. Таким образом, целевому устройству отводится, зачастую, весьма непритязательная роль неинтеллектуального преобразователя интерфейсов, через который PC работает с оконечным устройством. Представленная архитектура, по сути, представляет собой полноценный компьютер, и при наличии соответствующей программной поддержки часть или все функции по управлению оконечным устройством можно возложить на нее. Так как модули, интегрированные в рамках целевого устройства, зачастую, требуют простого управления, необходимо реализовать язык сценариев, доступный пользователям удаленно через стандартные средства визуализации.

|